728x90

플립플롭(Flip-flop)

래치(latch)와 동일하게 1 비트의 정보를 보관, 유지할 수 있는 회로

즉, 데이터를 저장하는 조합논리회로이다

래치와 차이점은 Clock유무인데 입력에 따라(level sensitive) 항상 반영되는 래치와는 달리 입력을 출력에 반영하는 시점을 클락(Clock,CLK,CK) 신호의 순간엣지(Edge-sensitive)에서 반영하는 플립플롭의 차이가 있다

- 플립플롭 ->synchronous(동기식)

- 래치(Latch) -> asynchronous(비동기식)

플립플롭 종류

- RS 플립플롭 (Reset-Set Flip-flop)

- D 플립플롭 (Data Flip-flop , Delay라고도함)

- T 플립플롭 (Toggle Flip-flop)

- JK 플립플롭

1. RS 플립플롭 (SR플립플롭)

기본적인 플립플롭이다 NOR게이트를 이용하여 만들 수도 있고 NAND게이트를 이용하여 만들 수 있으며

대표적인 특징은 R과 S가 동시에 1이 되면 안된다.

| R | S | Q | Q+1(다음출력) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 금지 |

| 1 | 1 | 1 | 금지 |

해당 진리표를 보고 RS는 이러한 특징이 있다는 것을 알 수 있다.

| R | S | |

| 0 | 0 | 불변(유지) |

| 0 | 1 | 세트(1) |

| 1 | 0 | 리셋(0) |

| 1 | 1 | 금지 |

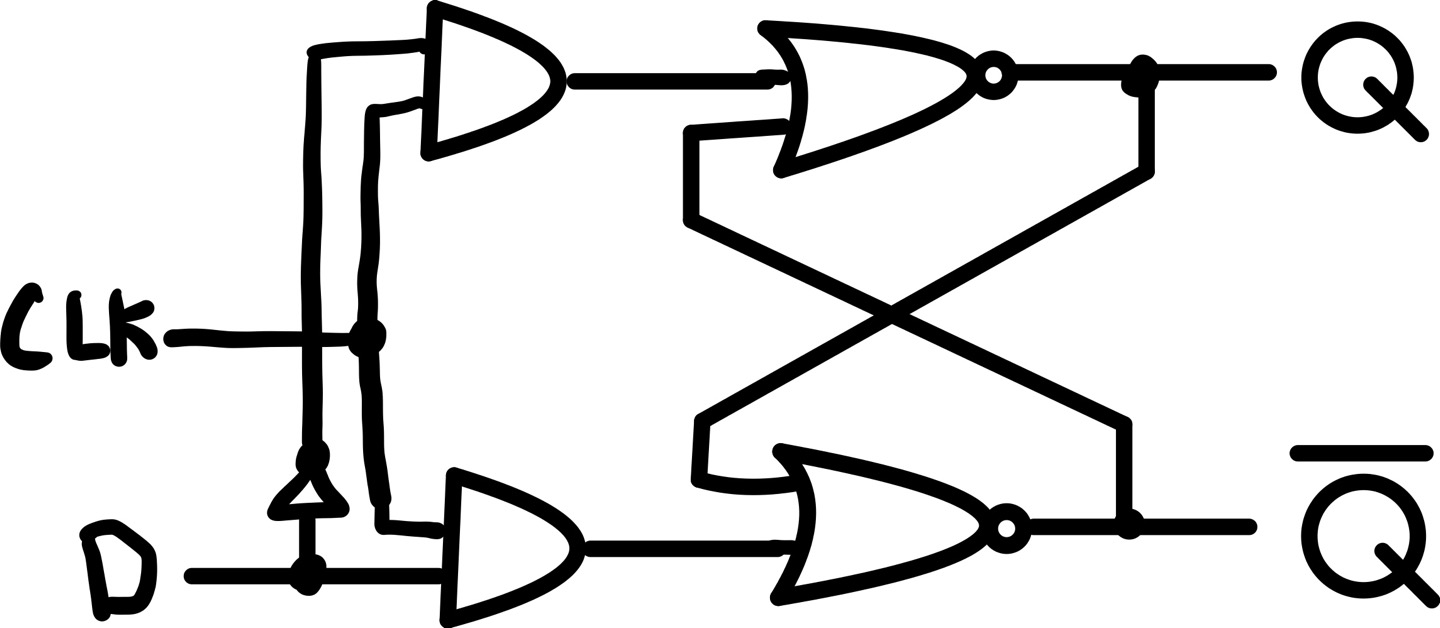

2. D 플립플롭

RS 플립플롭에서 R/S 1,0인경우를 피하도록 설계하였다.

RS에서 not을 추가하여 10 01의 입력만 가능하게 하였다.

아래 있는 논리회로는 Gate D 플립플롭이라고도 하고 Level-triggered D-Typr flip-flop이라고도 하는데

CLK(혹은 Hold bit)이 1일떄만 Data값을 저장한다는 의미를 가지고 있다.

| D | CLK | Q |

| 0 | 1 | 0(리셋) |

| 1 | 1 | 1(셋) |

| X | 0 | Q(현상유지) |

3. JK 플립플롭

RS 플립플롭에서 1 , 1 경우 토글(상태 반대로)를 추가한 것이다

| J | K | |

| 0 | 0 | 불변(유지) |

| 0 | 1 | 리셋(0) |

| 1 | 0 | 세트(1) |

| 1 | 1 | 토글(반전,보수) |

4. T 플립플롭

토글 플립플롭으로 불리며 입력이 들어오면 상태가 반전되는 플립플롭이다

| T | |

| 0 | 불변(유지) |

| 1 | 토글(반전,보수) |

728x90

'2.1 CS > 컴퓨터구조 & 논리' 카테고리의 다른 글

| [cs/컴퓨터구조&논리] Accumulator (0) | 2024.08.19 |

|---|---|

| [cs/컴퓨터구조&논리] Multiplexer, Demultiplexer, Encoder, Decoder (0) | 2024.08.19 |

| [CS/논리] Logic gate(논리게이트) (0) | 2024.08.13 |

| [컴퓨터구조] 폰노이만 구조 (0) | 2024.08.13 |

| [Cs/컴퓨터구조] RISC, CISC (0) | 2024.08.09 |

댓글